## ScanchainECO

—— 针对周转时间和测试覆盖率进行最优化的自动化扫描链 ECO

ScanchainECO Datasheet

DS-DFT-01

ScanChainECO 使用创新算法帮助设计团队高效完成扫描链 ECO 任务，同时尽量降低因 Functional ECO 而导致的测试覆盖率损失。基于用户的设计更改，ScanChainECO 会自动修正原始扫描链电路，更新后的扫描链电路拥有更高的测试覆盖率和与原来相同的测试效率。

### 解决方案的优势

- 防止因为 Functional ECO 等操作导致的测试覆盖率损失

- 易于使用并且可以提供最优化补丁来达成最佳扫描链实现效果

- 是一种即插即用工具，可轻松与第三方设计流程集成

### 扫描链 ECO 简介

扫描链 ECO 是 ECO (Engineering Change Order) 期间的重要步骤，它是一种用于修订现有 ASIC 设计的增量设计方法。一旦 RTL 代码被修改，有新的寄存器加入或者旧的寄存器被废除，扫描链 ECO 可以将扫描链进行局部的更新以适配这些寄存器的变化，同时保留其他大部分区域的电路特性。

ScanChainECO 在修改后的设计中，会将新的寄存器缝合进原有的扫描链中，以维持测试覆盖率。并将需被移除的寄存器从原有扫描链中移除，以增加后端的可绕性与最大程度上去减少设计密度。

传统上，DFT 工程师必须解决在 Functional ECO 任务中产生的扫描链漏洞。由于扫描链和测试模式通常由 ATPG 工具生成，DFT 工程师通常缺少一种有效的方法来根据 ECO 补丁报告中的更改进行必要的修改。他们必须使用 ATPG 工具重新检查错误原因，并重新参考既有的扫描链架构来修正 Functional ECO 所导致的 DFT DRC 错误。或者直接选择放弃新添加的寄存器，导致测试覆盖率降低与测试风险提高。或直接忽略已经无作用且可移除的寄存器，导致可能影响后端的布线性能与时序收敛。

ScanChainECO 赋予设计师高效执行扫描链 ECO 任务的能力，以应对设计中对寄存器的增减。

### ScanChainECO 设计流程

扫描链修复过程起始于对原始扫描链网表的精确分析。ScanChainECO 根据用户的设计约束修改扫描链。它可以

与用户的现有 ASIC 设计工具无缝集成，创建一个高效协作的互补流程。

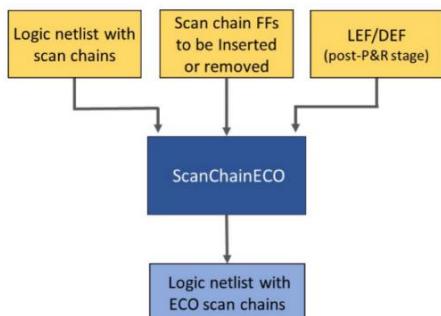

左图描绘了 ScanChainECO 工具流程，其中：

1. 需要进行增减的寄存器列表可以通过第三方 ECO 工具生成的报告得到（例如 EasylogicECO），或者是由用户为特定 ECO 案例手动创建的寄存器更新列表。

2. ScanChainECO 可以生成修正完毕的网表。网表中的扫描链已经对列表中的寄存器进行了必要的处理。

## ScanChainECO 特点

### Scan DFF 选择与转换

将常规 DFF 根据需要转换为可插入到扫描链中的 SDFF。

### 扫描链缝合，移除和平衡

将新增加的 SDFF 缝合到原始扫描链中，同时将已经废除的 SDFF 从扫描链中移除。根据用户的 DFT 约束来限制链长以满足测试要求，从而在不需增加测试成本的情况下提高测试覆盖率，并适当地减轻 ECO 对后端所造成的影响。

### 支持高级设计要求

确保在实施扫描链修正时遵循设计规则。可以识别多时钟域、根据需要在网表中增加 Lockup 器件、避免时间冲突。

### 支持各种不同的设计流程

ScanChainECO 可以支持在工程师手工进行 ECO 后得到的网表上进行操作，也可以嵌入 EasylogicECO 流程中同时完成 Functional ECO 和 ScanChain ECO 操作。还可以支持在第三方 ECO 工具生成的网表上进行 ScanChain ECO 操作。ScanChainECO 的输入输出均为标准文件格式，可以与现有主流设计流程的无缝集成。

### 命令行脚本操作

基于脚本的操作简单，易于学习和调试。迁移到其他项目时只需要修改特定的脚本字段即可。

## 技术支持

需要了解更多信息，请访问官网 <http://www.easylogic.com> 或者发送邮件至 [info@easylogiceda.com](mailto:info@easylogiceda.com)。

## 版权声明和专有信息

奇捷科技（深圳）有限公司版权所有 ©2020-2023。Easylogic 产品名称是奇捷科技的商标。Easylogic 产品和所有相关文档均为奇捷科技所有。未经书面同意，严禁复制、修改或分发 Easylogic 产品或相关文档。