奇捷科技(Easy-Logic),致力于提供电子设计自动化(EDA)领域高效的逻辑功能变更(ECO)解决方案,将于2025年6月22日-25日 美国旧金山举办的设计自动化大会(DAC 2025)上展示其最新技术成果 — 集成于其旗舰产品EasylogicECO工具中的突破性阶段性ECO设计环境,以更好的满足当今ASIC设计业快速演进的功能性ECO需求。

这些阶段性流程通过内置模块简化ECO操作,处理功能变更的同时,还能与用户ASIC设计流程无缝集成。相比传统方法, 这一创新,可以让ECO周转时间缩短50%以上。

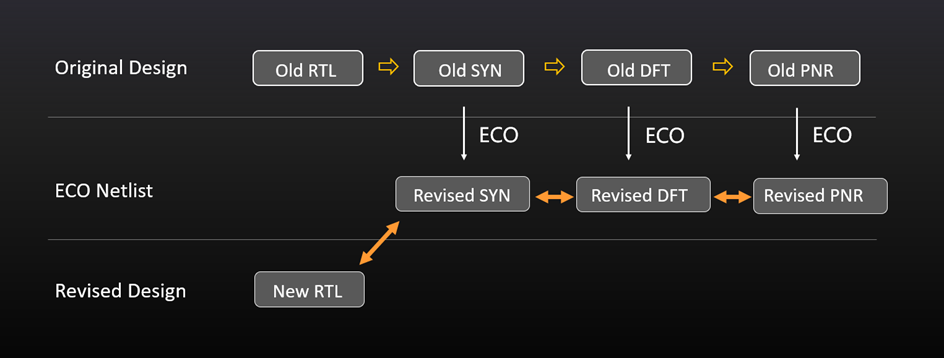

奇捷科技CEO魏星博士强调该方案的重要性:“在任何功能性ECO场景中,设计团队都面临层层挑战,首先是实现逻辑变更的复杂性;其次,每个设计阶段(综合、DFT、布局布线等)都需要适配其专属的ECO逻辑变更;最后,每次变更都需验证无误才能推进流程。这些难题会层层叠加,对项目周期和芯片质量构成多重障碍。EasylogicECO凭借其灵活性、效率和深度流程集成的特性,使ECO成为ASIC设计流程中高效且可控的一环,助力团队快速响应变更,确保质量与设计初衷不受影响。”

EasylogicECO 采用阶段感知架构,深度契合用户的 ASIC 设计流程,内置五套功能性 ECO 流程,每套流程精准映射常见的 ASIC 设计场景。 ECO 流程的每个阶段均包含具备嵌入式功能的操作模块和可配置开关,且同一设计流中的所有模块无缝协同,从而用户能够根据具体应用需求,进一步精准调控 ECO 结果。

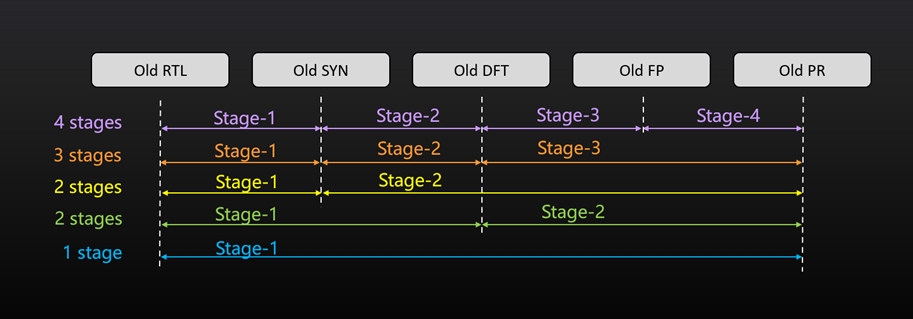

从具体应用场景来看,这些内置流程分别对应几种典型的 ASIC 设计模式,例如:

单阶段ECO流程(蓝色) :适用于小型数字电路设计(如混合信号ASIC),尤其是高频发生局部变更且ECO时间窗口极短需要快速响应的场景。

双阶段ECO流程(绿色) :为传统前后端团队的无缝协作而设计,前端工程师负责RTL设计、逻辑综合及DFT可测性设计全阶段工作,后端团队专注物理实现,该流程便于跨团队的高效协同。

双阶段ECO流程(黄色) :专为设计过程中需向后端实现团队动态移交RTL的场景而构建。

三阶段ECO流程(橙色) :专为大规模数字ASIC设计打造(如移动应用处理器/网络交换机)。该流程通过明确划分RTL设计、DFT团队与后端实现的职责边界,构建标准化ECO协作体系。所有变更需经综合与DFT阶段完成结果验证后,方可执行后端修改,从而最大限度降低风险。

四阶段ECO流程(紫色) :专为GPU或AI服务器芯片等超大型ASIC设计定制,适用于含多副本或层级化模块的芯片架构。其创新性在于新增布图规划环节——通过物理指引调整补丁逻辑,尤其针对模块间距影响时序路径的关键场景,在布局布线前完成优化。

我们的技术支持团队将在DAC展会中为参观来宾说明EasylogicECO如何无缝集成至现有设计环境并进行产品demo演示,同时我们也会针对不同的ECO应用进行探讨并提供定制化解决方案建议,在此诚邀业界同仁莅临洽谈。