EasylogicECO 产品目录

下载文档EasylogicECO—— 基于RTL修改而完成的自动化ECO设计流程,针对补丁大小和周转时间进行最佳优化

EasylogicECO Datasheet

DS-ECO-01

EasylogicECO使用创新的Functional ECO算法,可有效地完成ECO任务,减少项目周期的意外延迟。它基于用户的RTL更改对各个设计阶段已经完成的门级网表进行最小化修正,创建与更新后RTL逻辑功能一致的修正网表。

解决方案的优势:

• 基于RTL的修改推断门级网表的修改点,可以得到最小补丁逻辑。

• 适用于各种大小和复杂度的芯片设计,缩短ECO周期。

• 优化补丁时考虑对时序收敛的影响。

• 在Functional ECO的同时保持扫描链逻辑的完整性,也可以同时进行扫描链逻辑的更新。

Functional ECO(Engineering Change Order) 介绍

Functional ECO是用于修改现有ASIC设计的增量式设计方法。一旦RTL代码被修改,ECO流程将会修改原网表的一小部分,使得修改后的网表与修改后的RTL功能保持一致。由于ECO可以保留原网表大部分区域的电路特性,从而使得工程师无需重做,避免浪费大量时间。

近年来,随着ASIC设计的复杂性增加和项目周期的缩短,Functional ECO需求变得越来越普遍。当需要进行RTL更改时,如果重新完成整个设计流程很可能会导致项目延迟。Functional ECO为RTL变更提供了一条捷径。在设计阶段后期,一次成功的ECO任务可能避免项目数个月的意外延迟。

EasylogicECO 设计流程

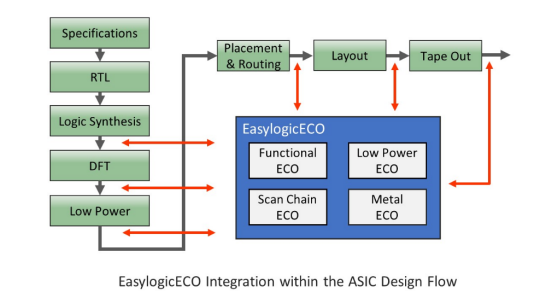

用户现有的ASIC设计流程可以与EasylogicECO无缝集成,使EasylogicECO成为现有设计流程上的有效补充。从准确分析RTL行为变化开始,使整个ECO流程更为细致与精确,避免用户直接在网表上进行修改。

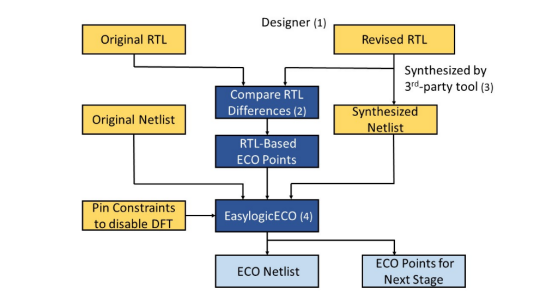

EasylogicECO流程有四个主要步骤:

1. 用户对RTL进行更改

2. 使用任何逻辑等价性检查工具识别RTL的功能变更

3. 对更改后的RTL进行逻辑综合生成参考网表

4. 在原始网表上进行ECO打补丁来创建一个新网表,并产生用于下游操作的设计约束

EasylogicECO 特点

1)使用突破性算法得到最佳ECO结果

使用已获专利的形式验证算法进行ECO流程,可以快速有效地完成ECO任务,获得最佳结果。

2)DFT支持

Functional ECO过程中自动保持扫描链的完整性。并且可以自动将新增的寄存器插入到扫描链中,或者将冗余的寄存器从扫描链中移除。在进行扫描链更新时,也会充分考量扫描链的物理性能等因素。

3)支持大模块更改

哪怕Block包含的逻辑单元数量巨大(例如包含几百万的逻辑单元),EasylogicECO也可以快速定位出需修改逻辑在电路中的准确位置。无需担忧运行时间问题,也无需将大的Block被迫切分为小的Block分别进行ECO。大大减少了用户的手工操作工作量。

4)支持先进的设计要求

在进行电路更改时,会确保遵循原始的设计规则。例如,ECO流程中会考虑DFT、时钟域中的影响,并进行必要的调整。在低功耗设计中,也会保持各个电压域的约束。

5)多种Spare Resources用于Post-mask任务

利用一切可用的物理资源完成post-mask ECO任务,提高ECO的成功率。资源选项包括备用单元(spare instance)、可编程逻辑单元(GA, filler cell)和网表中已经不再使用的冗余逻辑单元(redundant instance)。

6)全部设计阶段均支持的ECO设计流程

支持对ASIC任何设计阶段(SYN/DFT/P&R等)的网表进行ECO操作,可完美融入客户的原有设计流程。

7)命令行脚本操作

脚本操作简单、易于学习、使用和调试。与主流ASIC设计流程无缝集成,支持各种工艺节点。

技术支持

需要了解更多信息,请访问官网 http://www.easylogic.com或者发送邮件至info@eaylogiceda.com。