近期,美国商务部工业和安全局(BIS)对全球EDA三巨头实施对华断供政策,引发行业对芯片设计供应链稳定性的关注,面对外部环境的不确定性,让芯片设计企业直面一个现实问题——如何在技术封锁与波动中维持研发节奏?

奇捷科技作为EDA领域逻辑功能变更(Functional ECO)的技术引领者,为更好的应对断供挑战,今日起向用户正式开放免费的产品试用与评估服务。

在芯片设计后期,当遇到意料之外的逻辑功能变更需求时,工程师常面临两难选择:重新设计,则项目进度会大幅延迟,人力和资金成本也会大大增加;若采用传统手工修补,效率低下且易引入新风险。奇捷科技的EasylogicECO工具,正是为打破这一痛点而生,直击行业核心需求。

更小化逻辑改动:通过核心算法的持续迭代,Patch Size得到有效优化,在部分实际项目中,Patch Size仅为国际竞品的几十分之一。这意味着在进行设计变更时,奇捷科技的工具能够以更小的逻辑改动实现同样的功能,大大减少了对原有设计的影响,提高了设计的稳定性和可靠性。

显著缩短设计周期:奇捷科技的ECO工具通过革新的流程与核心算法,与传统工具相比,自动化程度大大提高,能够在更短的时间内完成复杂的工程变更,大幅提高了设计效率。

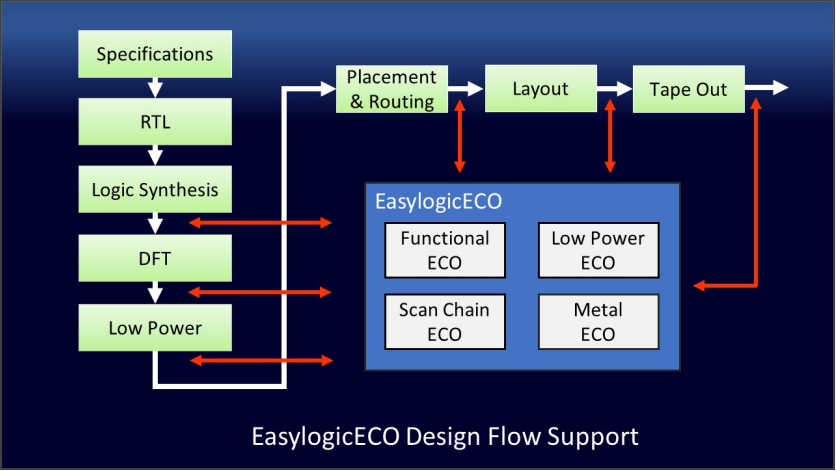

和现有设计流程无缝集成:奇捷科技的ECO产品不仅在技术上具有显著优势,还提供了一种高度适应性的ECO设计环境。EasylogicECO提供五种内置的功能ECO流程,每种流程都精确设计,从而可以和用户现有ASIC设计流程无缝集成。

EasylogicECO开放免费试用的软件包括:

EasylogicECO Function

支持大规模的ASIC设计,可在较短项目周期内,对不同设计阶段的RTL/Netlist应用不同的独创算法,快速获得最小的、最优的补丁逻辑,一次成功的ECO任务将显著减少项目的延误,周期从几个月缩短到仅几天。

EasylogicECO ScanChain

在不影响功能逻辑的前提下,支持对扫描链进行灵活的上链、下链、对比、可控时钟/复位以及DFT DRC检查和修复等功能,避免因功能逻辑变更导致的DFT逻辑错误或覆盖率下降问题。

EasylogicECO Metal

支持对投片之后的ASIC设计,通过仅改变金属连线的方式进行ECO。支持丰富的备用资源类型,包括传统的spare cell/instance以及先进的gate array filler的方案,同时,高效的算法对补丁逻辑进行基于物理位置的优化,可获得最佳的时序和布线结果。

奇捷科技的ECO解决方案已为全球众多用户提供切实支持,如您想了解更多产品信息,或者进行软件试用,欢迎联系我们,我们将安排技术支持团队和您进行需求沟通:

方式一:邮箱 info@easylogiceda.com

方式二:扫码提交您的公司名称、联系人姓名、联系方式及所在城市,我们将尽快与您联系

奇捷科技始终相信,EDA工具的价值应回归本质——用更优的解决方案帮助客户创造商业成功。无论外部环境如何变化,我们将以持续的技术创新,与行业伙伴共同构建不依赖单一技术路径的竞争力。