执行功能性ECO时的扫描链修复

下载文档EasylogicECO应用说明 App-DFT-01 | EasylogicECO在DFT方面给使用者带来3大效益: 1. 自动上链, 2. 自动平衡扫描链的链长,以及 3. 手工指定上下链方式, 因此显着缩短每一次功能性ECO所需要的时间。这篇应用说明简单介绍EasylogicECO如何处理需要新增或移除的Scan DFF。

概述 一般而言,在功能性ECO后若在扫描链上有新增或刪除的DFF,則使用者必须以手工方式来达成上下链。如果新增或刪除的DFF数量不多,手工仍能达成工作,一旦异动的DFF数量增多,則必須耗费大量时间去追踪相关的扫描链信息例如 scan clock source,每一个链长,扫描相关功能,compressor circuit等。修复扫描链不仅是一项非生产性的工作,而且是一项非常复杂的工作,这些工作往往超越人力范围,导致使用者只能放弃这些异动过的DFF之DFT coverage,甚至因此放弃ECO。在DFT的修复方面,Easylogic 的解决方案可提供极大的协助。 |

EasylogicECO 的主要功能

在以下四方面EasylogicECO可产生极佳的使用效果,

1. 自动上下扫描链 (Scan Chain Stitching)

2. 自动的链长调整 (Scan Chain Balancing)

3. 附带的手工调整功能 (Optional Manual Stitching)

4. 手工排除被拼接进扫描链的寄存器。

以下分标题详细说明。

(1) 自动上下扫描链 (Automatic Scan chain stitching)

自动上下链的功能帮助使用者以最短时间完成扫描链ECO,避免在繁琐的扫描链处理过程中产生人为错误。

依据使用者下的Disable DFT约束, EasylogicECO內建的演算法先把逻辑功能與DFT功能区隔开来。再依据使用者宣告的compressor tail input pin 來追踪相关的扫描链。若是有需要移除的SDFF,则会将此颗SDFF的SDFF/Q与SDFF/SI相连,达到下链目的。相反的,若有新增的DFF需要上链,则会根据新增DFF的parent module中的扫描链状况,例如 clock source和chain length,來判断是否有合适位置可以把新增的DFF自动缝合上,以达成自动上下链目的,并且保证可以符合DFT之DRC要求。

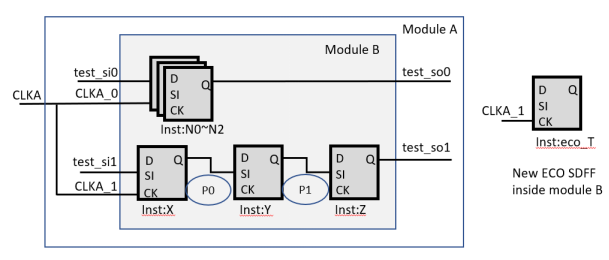

以下图为例 (图1),如果X、Z连接到compressor电路,ECO新增DFF的clock source是CLKA_1且在module B內,EasylogicECO会把新增的DFF接在P0或是P1上。如果P0较接近整条链的中间点,则就会把eco_T连接在P0位置,则连接在P1。

图1: 自动将新增的ECO SDFF拼接到P0或P1

(2) 自动链长调整 (Automatic chain length balancing)

自动链长调整除了节省ECO的时间外,更能确定使用者的芯片测试成本不会因为做了ECO而增加。

如前段所提到,EasylogicECO会依照使用者的相关设定自动追踪所有扫描链的长度,再依据新增DFF的clock source与parent module来判断如何连接新增的ECO DFF到既有的链上,并且确定扫描链的长度在要求的范围之内。使用者可以宣告set_max_chain_length来限制芯片所有扫描链的长度,这也会对balancing产生作用。若是无法满足上链的条件 (如max chain length或same clock source的要求) 则会判断fail,并显示于log file中。

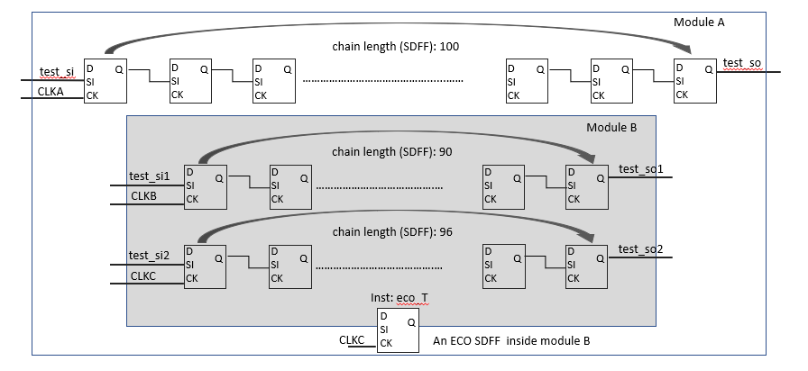

以下图为例 (图2) ,假设最长的链长是100,而ECO新增DFF的clock source是CLKC且在module B内,eco_T会被接在test_si2到test_so2的中间位置,也就是第49的位置。

图2: 自动平衡链长

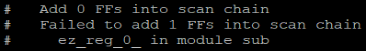

同样的,在上下扫描链时,EasylogicECO若无法达成使用者宣告的maximum chain length值,则会直接放弃并在log文档中显示,以下是log的例子 (图3)。

图3: 放弃自动平衡链长

(3) 附带的手工调整功能 (Optional Manual Stitching)

手动上下链是一个附加功能,赋予使用者在遵守公司特定的DFT设计规范上更大的ECO自由度。

使用者可以在EasylogicECO 的环境里精准宣告chain member的接法。这个用法适用于如下的场景:

a. EasylogicECO无法完成上下链的要求 (scan chain stitching failed)

b. 时延超标 (Timing issue)

c. 布局布线过于拥挤 (P&R congestion issue)

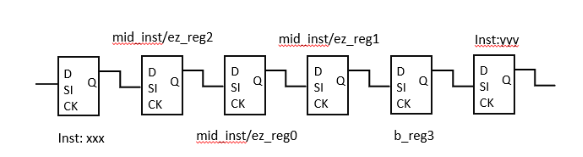

以下的例子中 (图4),原始的扫描链次序为 xxx/Q →b_reg3 → yyy/SI |

图4: 原始扫描链 |

使用者在确定一个适当的SDFF位置后(如b_reg3),可指定将新的 SDFF拼接在该位置,并使用以下命令宣告chain member的接法

insert_reg_into_scan_chain mid_inst/ez_reg[1] b_reg[3]

insert_reg_into_scan_chain mid_inst/ez_reg[0] mid_inst/ez_reg[1]

insert_reg_into_scan_chain mid_inst/ez_reg[2] mid_inst/ez_reg[0]

需注意的是,insert_reg_into_scan_chain是有顺序性的,必须由后方member(b_reg3)先宣告完,才能接着往前方member(ez_reg2)宣告。最终的链序列是

xxx/Q→ez_reg2→ez_reg0→ez_reg1→ez_reg3→yyy/SI (图5)

图5: 手动缝合链条

(4) 排除被拼接进扫描链的寄存器

手动排除已经被上链了的SDFF是一个附加功能,赋予使用者在遵守公司特定的DFT设计规范上更大的自由度。

使用者可以宣告保留或排除一个指定的寄存器。这个用法适用于如下的场景:

a. 时延超标 (Timing issue)

b. 布局布线过于拥挤 (P&R congestion issue)

c. 自定义的特殊扫描链功能 (User-defined special scan chain function)

d. 时钟产生线路 (Clock generating circuit).

可使用如下命令防止特定寄存器被拼接进原始扫描链:

exclude_add_sdff mid_inst/ez_reg[1]

并可使用以下命令防止从原始扫描链中删除特定的寄存器:

exclude_remove_sdff redundant_occ/shift_reg

总结

在EasylogicECO的自动化流程下,修改DFT的工作变得简单。 EasylogicECO的DFT效益包括

• 自动上下链,免除人工追踪扫描链的困扰,即使大量SDFF的上下链也没有困难。

• 提供多样性的控制功能,使用者可以更灵活的达成DFT相关设计要求。

• 显着缩短每一次功能性ECO所需要的时间, 逻辑功能设计加上DFT也是一次作业运行就可解决。